프로세서 7 - 데이터 해저드

안녕하세요! WH입니다.

컴퓨터 구조론 정리해야지 해야지 하면서 미뤄왔는데,

진작 했으면 안해도 되었겠죠?

그렇지만 지금이라도 하니까요! 얼른 끝내 봅시다.

오늘은 명령어를 먼저 보면서 시작해 볼게요

명령어

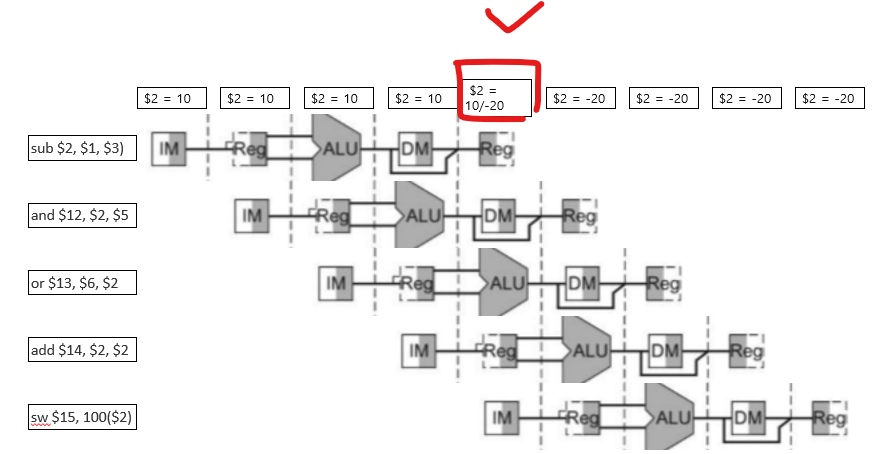

1. sub $2, $1, $3 $ # Register $2 written by sub

2. and $12, $2, $5 # 1st operand($2) depends on sub

3. or $13, $6, $2 # 2nd operand($2) depends on sub

4. add $14, $2, $2 # 1st ($2) & 2nd($2) depends on sub

5. sw $15, 100($2) # Base ($2) depends on sub

이 명령어의 의도는 뭘까요? 우선 기본적으로 2-5 명령어는 첫 번째 명령어에 종속적이네요? 첫 번째 명령어에 따라 다른 모든 명령어가 바뀌길 바랐을 겁니다. 예를 위해서 sub 의 결과는 10 -> -20으로 바뀐다고 가정하겠습니다.

이를 데이터 패스와 함꼐 볼까요? sub가 실행되고 5번째 CC ( clock cycle )에서 $2의 값이 바뀝니다. 10 -> -20으로 말이죠. 그럼 우선 sub와 add 는 CC 5에서 Reg를 쓰고 있으므로 해저드가 발생할 수 있습니다. 그러나 이는 하드웨어적 설계로 해결할 수 있습니다. sub는 쓰기를, add 읽기를 시행하죠. 즉 설계시에 가정을 하는 겁니다. 레지스터를 반으로 나눠서 쓰기는 앞에서 읽기는 뒤에서 한다고요. 그럼 겹치는 부분 없이 해결이 가능하겠죠?

아 그래서 뭐할라고 이걸 가져온건데요? 집중하시길 바랍니다.

프로그래머 의도 : 2, 3, 4, 5 명령어 모두 $2 = -20 이라는 값을 의도 했습니다.실제 프로그램 : add 와 sw 를 제외한 나머지는 의도처럼 되지 않았다.

즉 and 와 or 는 CC 4와 CC 5 에서 reg 의 내용을 읽어 옵니다. 그래서 -20이 아닌 10 을 읽어오게 되는 것이죠. 이렇게 현재 수행중인 명령어가 이전 명령어에 종속되어 해저드가 발생하는 상황을 데이터 해저드라 합니다.

그럼 이런 데이터 헤저드는 어떻게 제거하냐. 크게 4가지 방법이 있습니다.

1. 전방전달

- 레지스터 파일에 반영되기 전에 EX 단계에서 계산된 결과를 다음 인스트럭션의 수행단계로 전달 ( 추가 H/W 필요 )

2. 지연

- 컴파일러 수준에서 해저드 발견하고, no-operation 명령어 삽입 후 기다리면 됩니다.

3. 비순차 실행

- 접근 중인 데이터와 관련 없는 명령어를 삽입하여 실행하고, 이후 레지스터를 바이패스하면 됩니다. ( 컴파일러 수준에서 코드 실행을 변경합니다 )

4. 프로그래밍 방식

- 변수를 늘리거나, 계산이 완료된 후 한번에 실행하는 방식으로, 레지스터를 고려하여 프로그래밍하면됩니다.

코딩 내용을 써드릴까하다가.. 뭐 거기까지는 필요 없을 듯하여서 뺐습니다.

데이터 해저드가 무엇인지 알고가는 글이 되셨길 바랍니다. 이상 WH 였습니다.